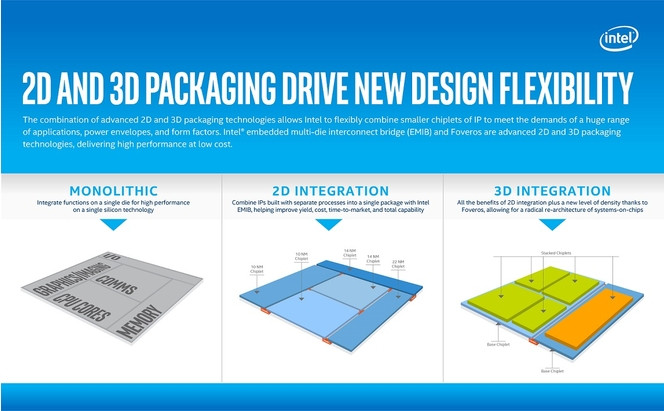

Le groupe Intel avait déjà commencé à combiner des composants exploitant des noeuds de gravure différents avec sa technologie EMiB (Embedded Multi-Die Interconnect) mais qui impose de les juxtaposer en plusieurs dies (2D stacking).

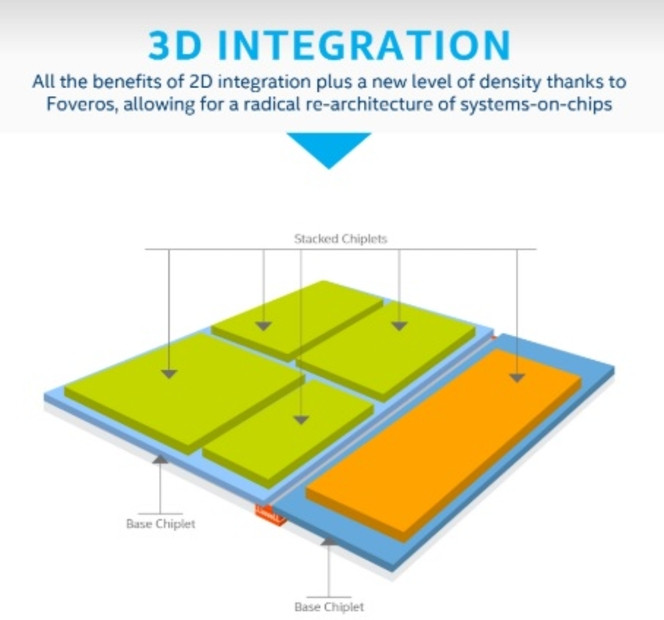

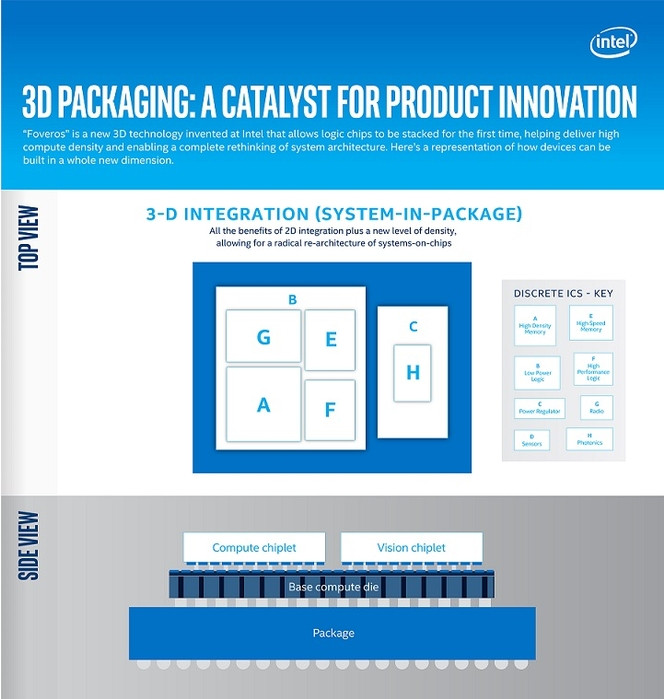

L'étape suivante n'est autre que l'exploitation de chiplets avec différents noeuds de gravure sur le même die grâce à la technologie Intel Foveros tout juste officialisée, avec la possibilité de superposer des composants offrant des finesses de gravure différentes (3D stacking).

Le principe a l'avantage de permettre d'utiliser le noeud de gravure le plus efficace (en terme de performance ou de prix, selon les besoins) en fonction des composants, comme par exemple les coeurs du CPU en 10 nm tandis que les autres composants peuvent être gravés en 14 ou 22 nm.

Comme dans le cas de l'architecture Zen 2 d'AMD, qui emploie aussi des chiplets (en 7 nm pour les coeurs du CPU), il est ainsi possible d'apporter une certaine souplesse dans le développement des plates-formes et de pouvoir intégrer plus rapidement les évolutions des composants.

Intel pourrait par ailleurs utiliser à la fois les technologies EMiB et Foveros pour certains ensembles de composants, offrant ainsi un plus large panel de combinaisons possibles pour ses futurs processeurs.

L'officialisation de la technologie Foveros a été l'occasion de montrer un CPU Hybrid x86 combinant à la fois un coeur Sunny Cove (gravé en 10 nm) et 4 coeurs Atom, le tout associé à un composant I/O gravé en 22 nm et rassemblé au sein d'un même package.

Habituellement, c'est plutôt du côté de l'architecture ARM que l'on trouve des combinaisons de différents coeurs au sein d'un même SoC. On retrouve là des avantages similaires, notamment en matière de consommation réduite en veille, tout en garantissant de la puissance en fonctionnement actif. A voir si cela donnera lieu à de nouvelles séries de processeurs.