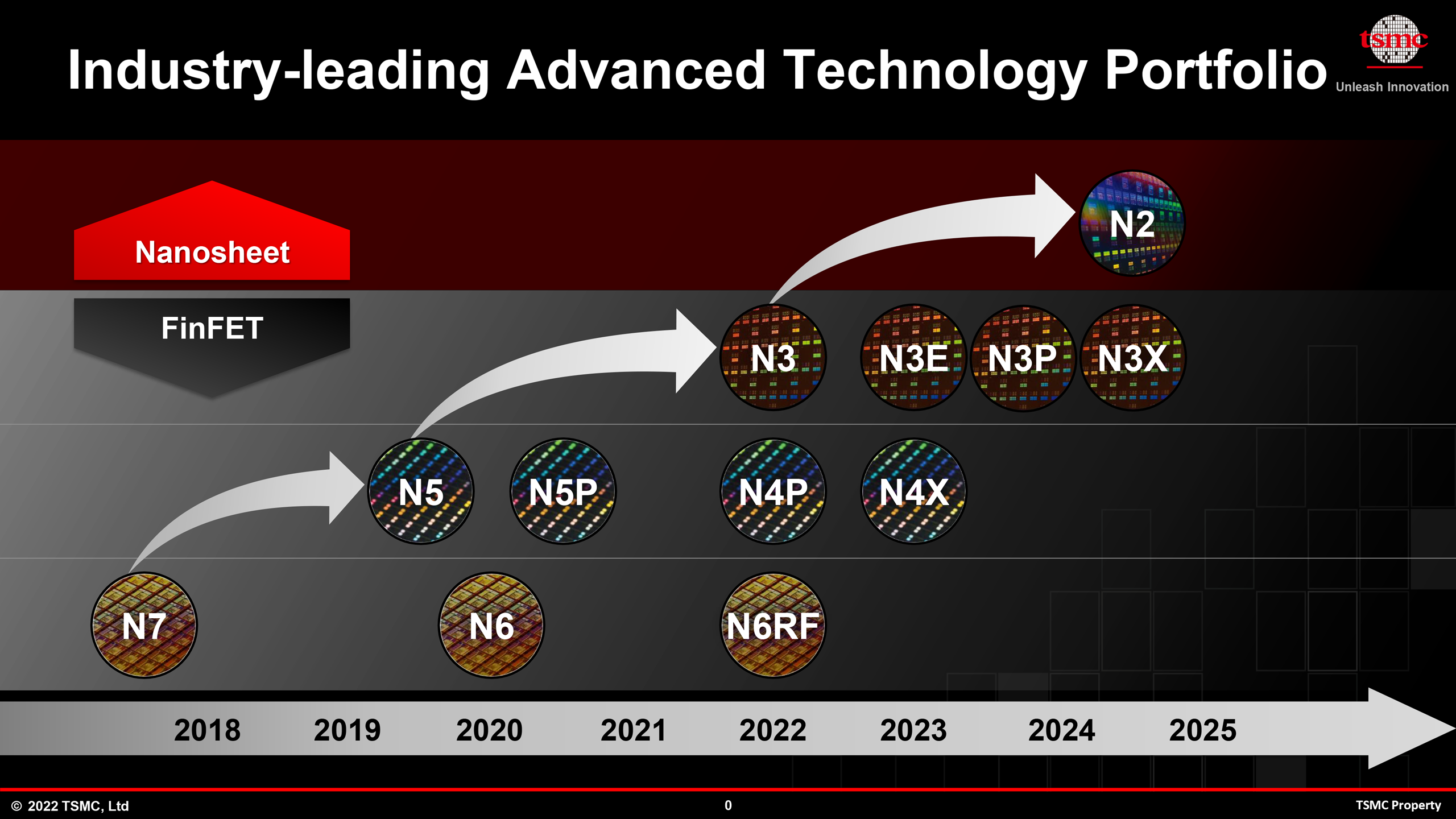

Le fondeur taiwanais TSMC entend conserver son leadership sur le secteur en maintenant la pression sur le noeud 3 nm tout en essayant de proposer aussi rapidement que possible une transition vers le 2 nm.

Pour couper l'herbe sous le pied de la concurrence, la firme est restée sur des transistors FinFET pour sa gravure en 3 nm qu'elle compte maintenir sur les trois prochaines années au moins grâce à des optimisations progressives.

La gravure en 3 nm FinFET a encore de beaux jours devant elle

Elle passera ainsi de la technique N3 initiale qui sera proposée sur le second semestre à des évolutions N3E, N3P et N3X jusqu'en 2024-2025. Si N3 est destinée aux clients les plus pressés, la technique N3E sera particulièrement intéressante en augmentant les performances de 18% et en réduisant la consommation d'énergie de plus de 30% par rapport à l'actuel noeud N5.

N3E va démarrer les tests de pré-production cette année et sera disponible vers mi-2023, pour des puces dans les appareils électroniques à la fin de l'année prochaine.

Les noeuds suivants continueront de raffiner le processus à mesure qu'il gagne en maturité mais de façon plus modeste, les limitations des transistors FinFET à ce niveau de finesse se faisant ressentir.

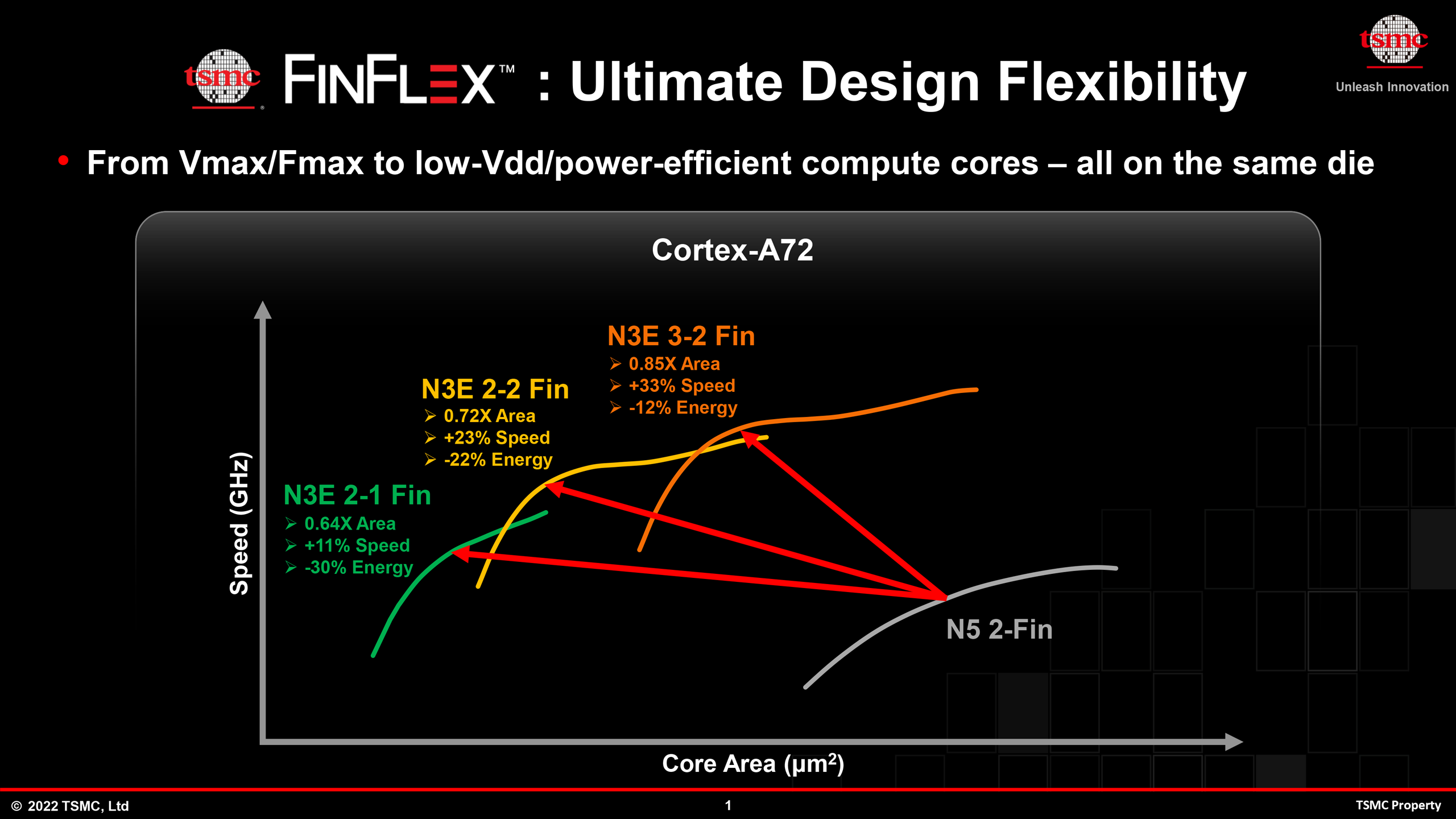

TSMC proposera d'ailleurs une technologie FinFlex qui permettra aux concepteurs de puces de personnaliser le profil des transistors pour créer des coeurs en fonction des besoins (classiquement choisir entre puissance ou économie d'énergie) au lieu d'un type unique de transistor FinFET sur le noeud 5 nm.

La gravure en 2 nm grâce aux transistors GAAFET

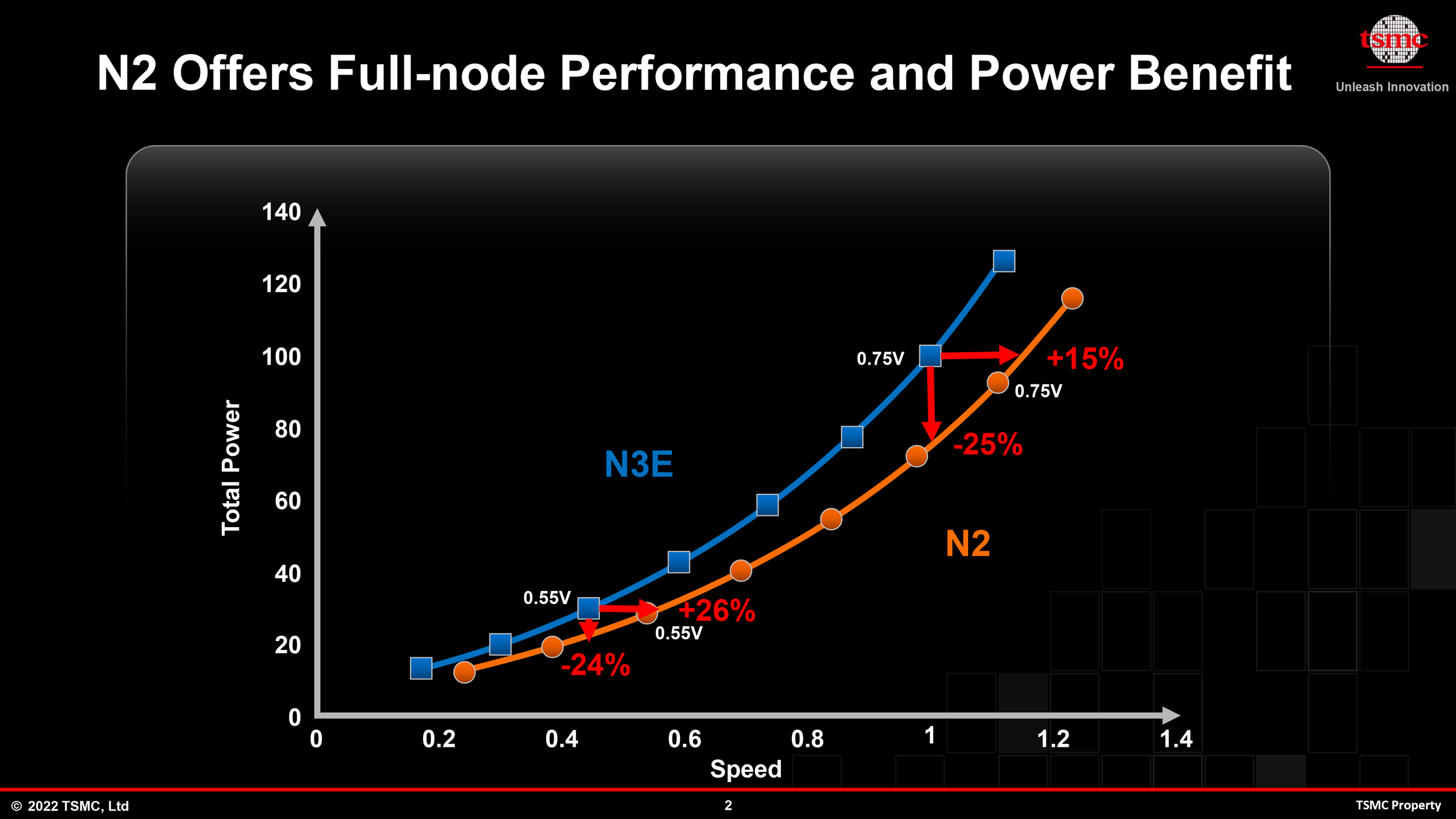

Ce n'est qu'avec le passage à la gravure en 2 nm que le fondeur troquera les transistors FinFET pour du GAAFET (Gate All Around FET), un nouveau type de transistor plus adapté pour la gravure très fine, notamment en matière de réduction des courants de fuite et en adaption plus fine des réglages entre performance et consommation d'énergie.

La promesse est d'améliorer encore les performances de 10 à 15% à nombre de transistors égal ou de réduire la consommation d'énergie de 25 à 30% à fréquence similaire par rapport à N3E avec une densité de transistors qui n'augmentera pourtant que de 10% environ, ce qui risque de marquer un point d'inflexion pour la progression des performances de certains composants comme les GPU et accélérateurs graphiques.

La progression de la densité sera tellement limitée que TSMC devrait proposer un noeud N3S similaire sur ce point avec sa gravure en 2 nm, ce qui constituera une première, indique AnandTech.

TSMC devrait également faciliter l'utilisation de la gravure en 2 nm pour une intégration dans des chiplets, au sein de systèmes présentant des composants avec différentes gravures sur le même die, ce qui est en train de devenir une tendance au sein de l'industrie, tant pour les CPU que les GPU.

La gravure en 2 nm entrera en pré-production au second semestre 2024 et devrait donc passer à la production de masse en 2025. Les premiers équipements électroniques à en profiter seront sans doute commercialisés fin 2025 ou plus vraisemblablement durant l'année 2026.